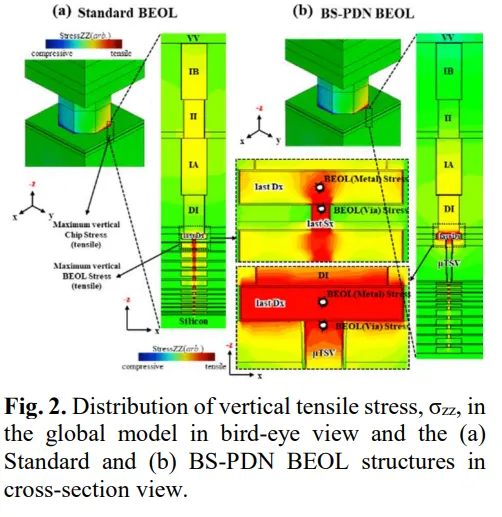

Reverse power distribution network (BS PDN) for next-generation chips is a well-known and widely discussed advantage of future technology. While Intel and TSMC have been talking about the BSPDN for a while, Samsung only recently shared details on their power experiments. It seems that the company expects quite obvious advantages from this innovation.

According to The El, in a paper presented at the VLSI Symposium at the end of June, Samsung Electronics reported that the use of the back-end power network resulted in a 14.8% reduction in processor area exposed compared to traditional front-end PDN. Meanwhile, the article specifically highlights the two Arm contours, where they observed a reduction in area of 10.6% and 19%, respectively. A 10-19% reduction in die area is a huge advantage as it allows you to pack 10-19% more transistors and improve performance or lower the cost of a particular chip.

Another thing Samsung mentions in its article is a 9.2% reduction in cable length. A back power bus usually allows for thicker wires with less resistance and can therefore draw higher currents for better performance. Further reduction in cable length will also provide additional performance benefits.

Additional rear power benefits that Samsung reveals are the design technology common optimization buttons that increase Fmax by 3.6%, reduce the area of the standard unit by 2.4% and increase the performance of the standard unit by 1.6%.

Earlier this year, Intel detailed the PowerVia backend power network, which will be used for 20A fabrication technology (2nm class) and beyond. The benefits of using a rear power bus are widely accepted, and Samsung’s findings support this theory. Power cables can be made more robust by moving the power busbars back and isolating them from the I/O cables. This thickening reduces resistance in the final stages of production, increases productivity and reduces energy consumption. In addition, this separation results in a reduction in logical space, resulting in cost savings.

Samsung did not disclose when and with which node it plans to implement the BS PDN. The company is currently developing 3nm class SF3 fabrication technology based on 2nd generation SF3 transistors and plans to use it for mass production in 2024. The company also has SF3P and 2nm class SF2, which will be released in 2025. It is unlikely that Samsung will use the rear power bus for the SF3 next year, the company may consider implementing its BS PDN on the SF3P or SF2 in 2025.

stay on the front lines

Join the experts who have read Tom’s Hardware for over 25 years for insider information on curious computer news. We’ll deliver breaking news and in-depth reviews of CPUs, GPUs, AI, manufacturer hardware and more straight to your inbox. Source